在ChatGPT的帮助下,他们不仅设计出CPU上的一个组件,甚至还通过了有效性验证环节。

这个组件主要负责创造出一种基于八位累加器的微处理器架构的逻辑。而累加器本质上是寄存器(存储器),是专门存放算术或逻辑运算的一个操作数和存储运算结果的。这是CPU运作中不可或缺的一部分。其中一个阶段是用硬件描述语言(HDL)(例如Verilog)描述芯片内不同部件的实际几何形状、密度和整体布局。在此前,作为一个极其专业化和复杂的领域,HDL编写一直是一项相对罕见且非常难以掌握的工作。

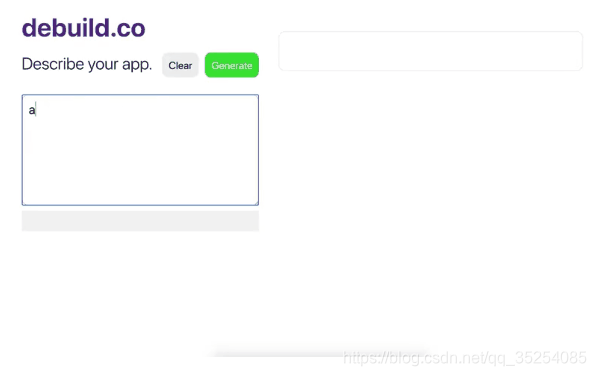

这也就意味着,即使是最好的工程师也还是经常需要用这种语言做一些琐碎的事情。而ChatGPT作为一种模式识别器,可以在各种类型的语言中转换自如,这就可以帮助工程师们跳过HDL阶段。在这项研究中,研究人员分别使用LLM对八个具有代表性的硬件设计示例进行了研究。工程师与LLM之间实时来回交互,将纯英文文本逐步转化为Verilog(HDL)的等效代码。

其中一位硬件工程师与LLMs共同设计了一种新颖的基于八位累加器的微处理器体系结构。他们将这些基准测试和处理器发送到Skywater 130纳米Shuttle进行流片(tapeout)。

这个过程中,研究人员评估了ChatGPT-4、ChatGPT-3.5、Bard、HuggingChat四个不同LLM创建硬件设计的Verilog能力.

特别声明:以上内容(如有图片或视频亦包括在内)为自媒体平台“网易号”用户上传并发布,本平台仅提供信息存储服务。

Notice: The content above (including the pictures and videos if any) is uploaded and posted by a user of NetEase Hao, which is a social media platform and only provides information storage services.

原文链接:https://www.163.com/dy/article/I8QBG1E505527A6C.html

评论 ( 0 )