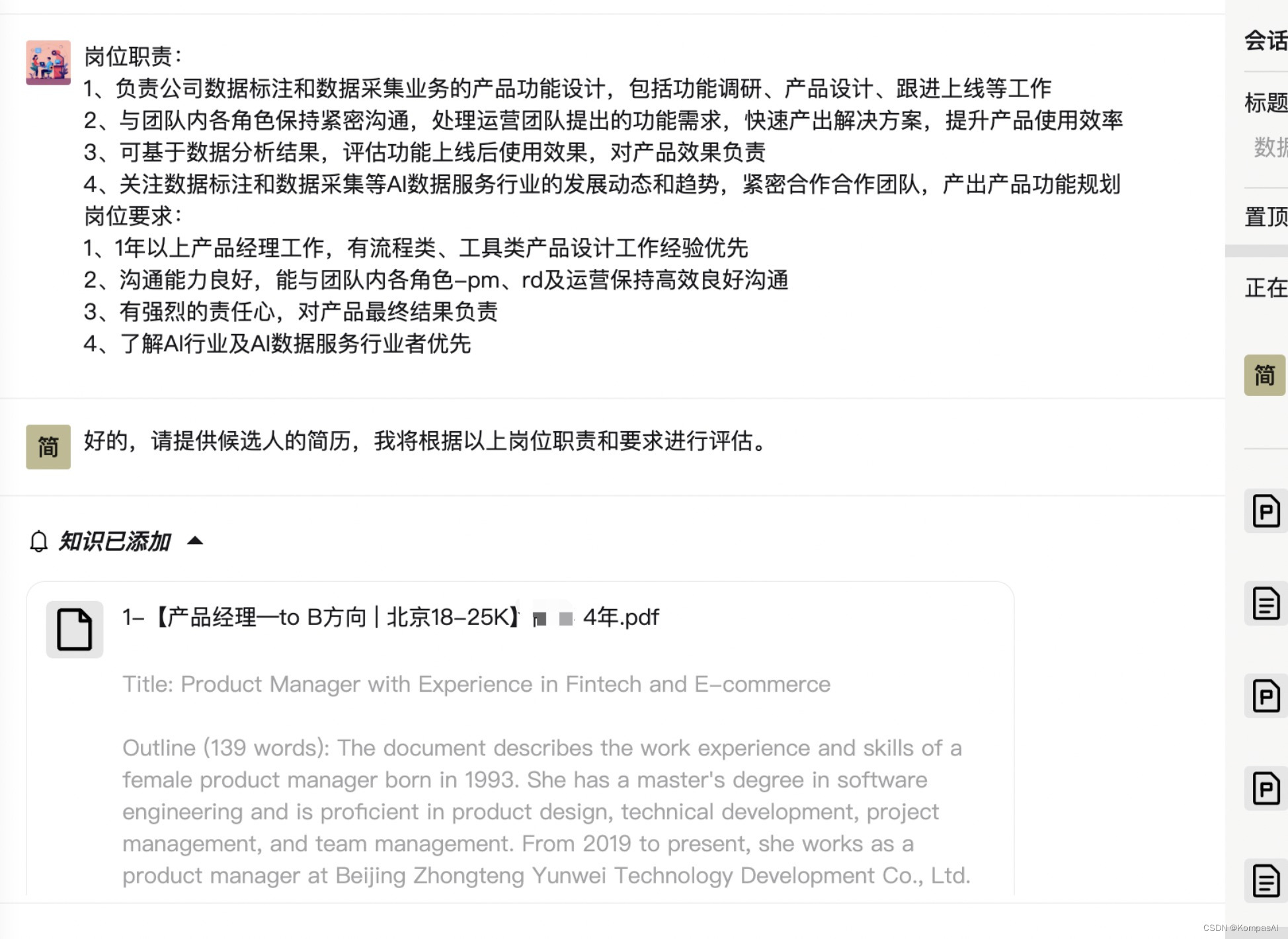

前言

阿里平头哥在高性能处理器与AI芯片主要有玄铁处理器、含光人工智能芯片、羽阵RFIC系列、倚天处理器芯片、无剑SoC。

结合最近几年阿里平头哥在HotChips、ISCA发布的报告和论文,总结了含光800-NPU加速器、玄铁810处理器-RISC-V硬件架构,可作为学习、研发高性能处理器与AI芯片的参考资料。本人才疏学浅,如有错漏之处,敬请指正。

1. 含光800

含光:上古三剑,一曰含光;视不可见,运之不知其所处;泯然无际,经物而物不觉。

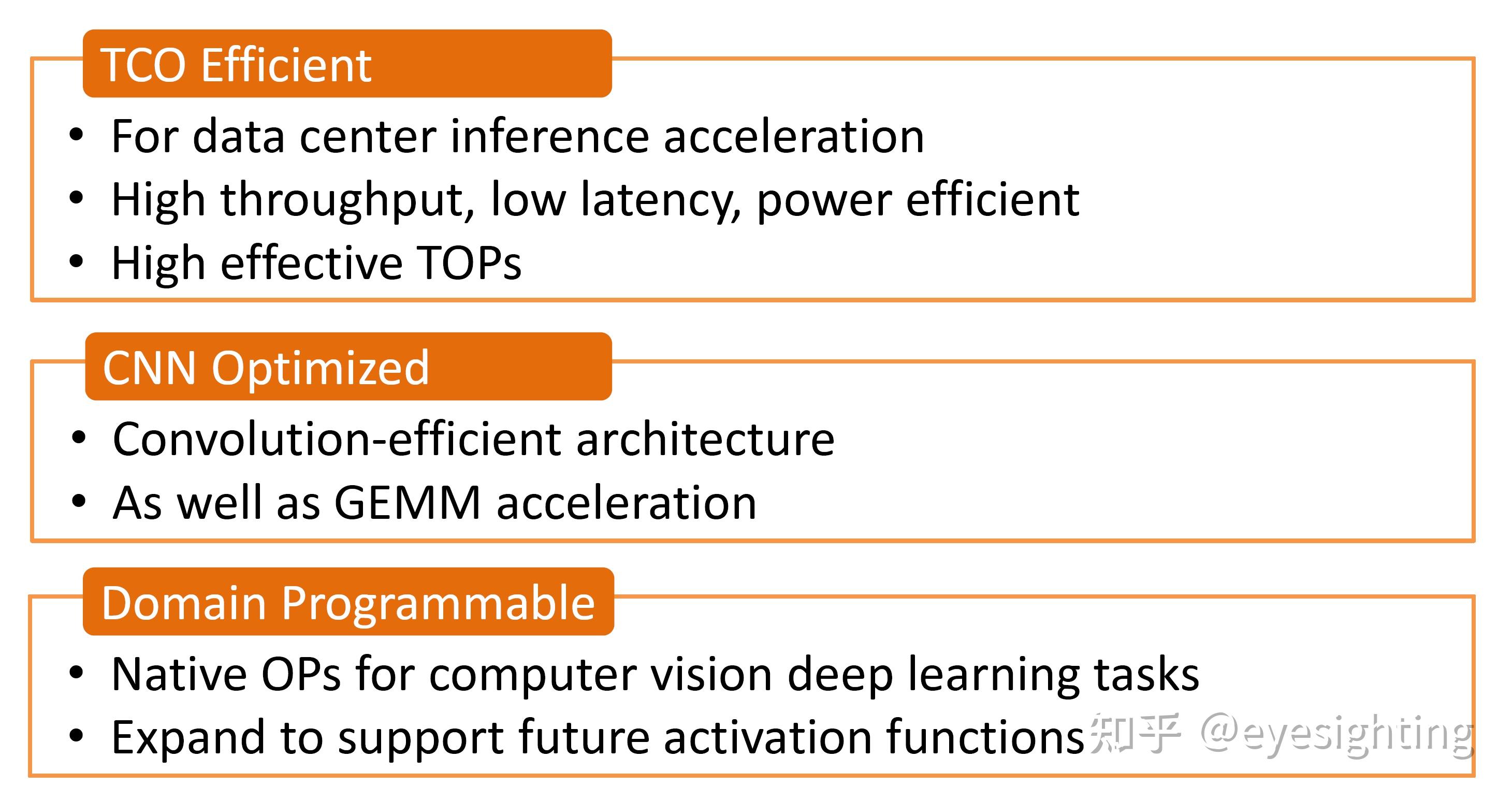

商业驱动的设计

系统框图

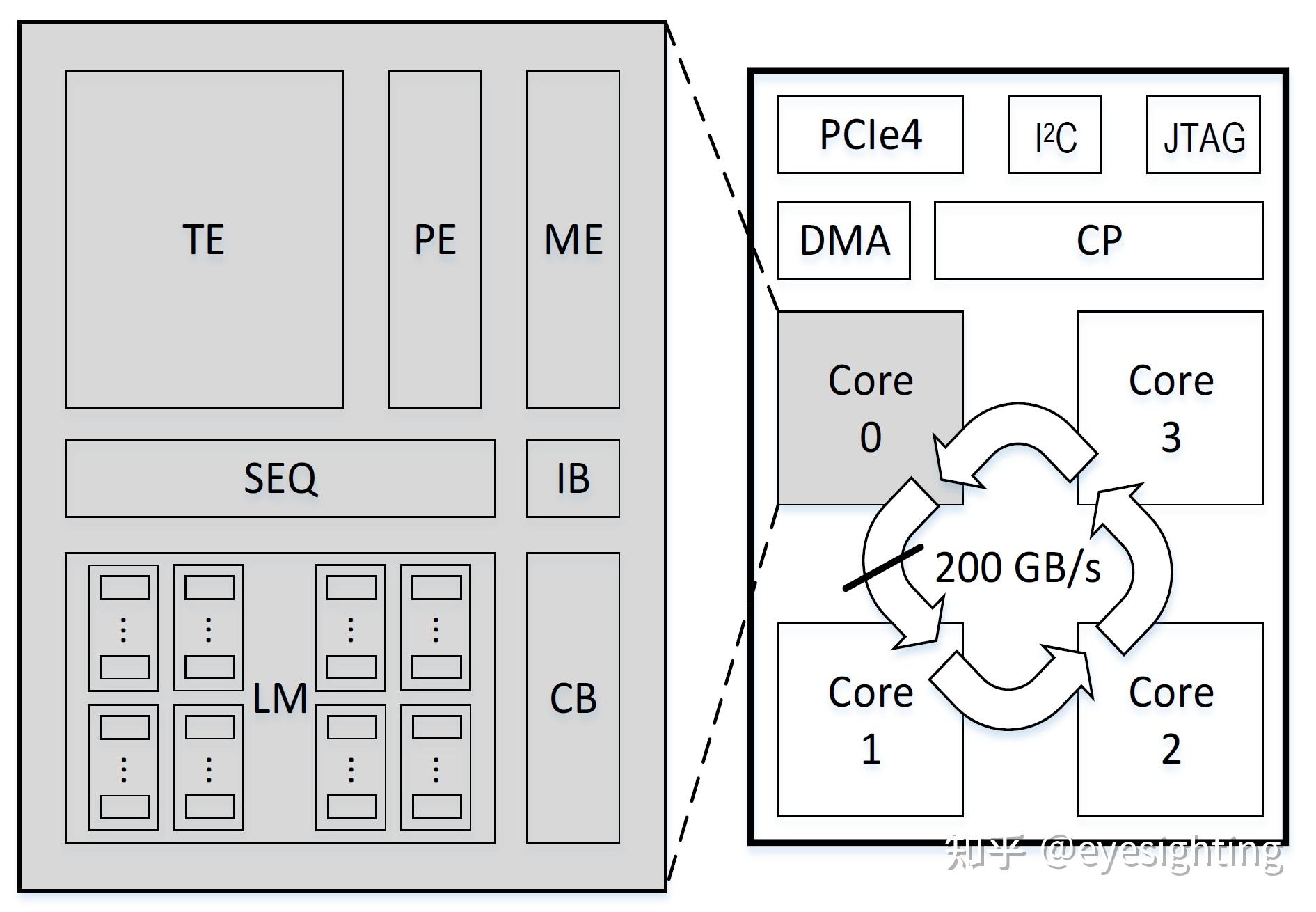

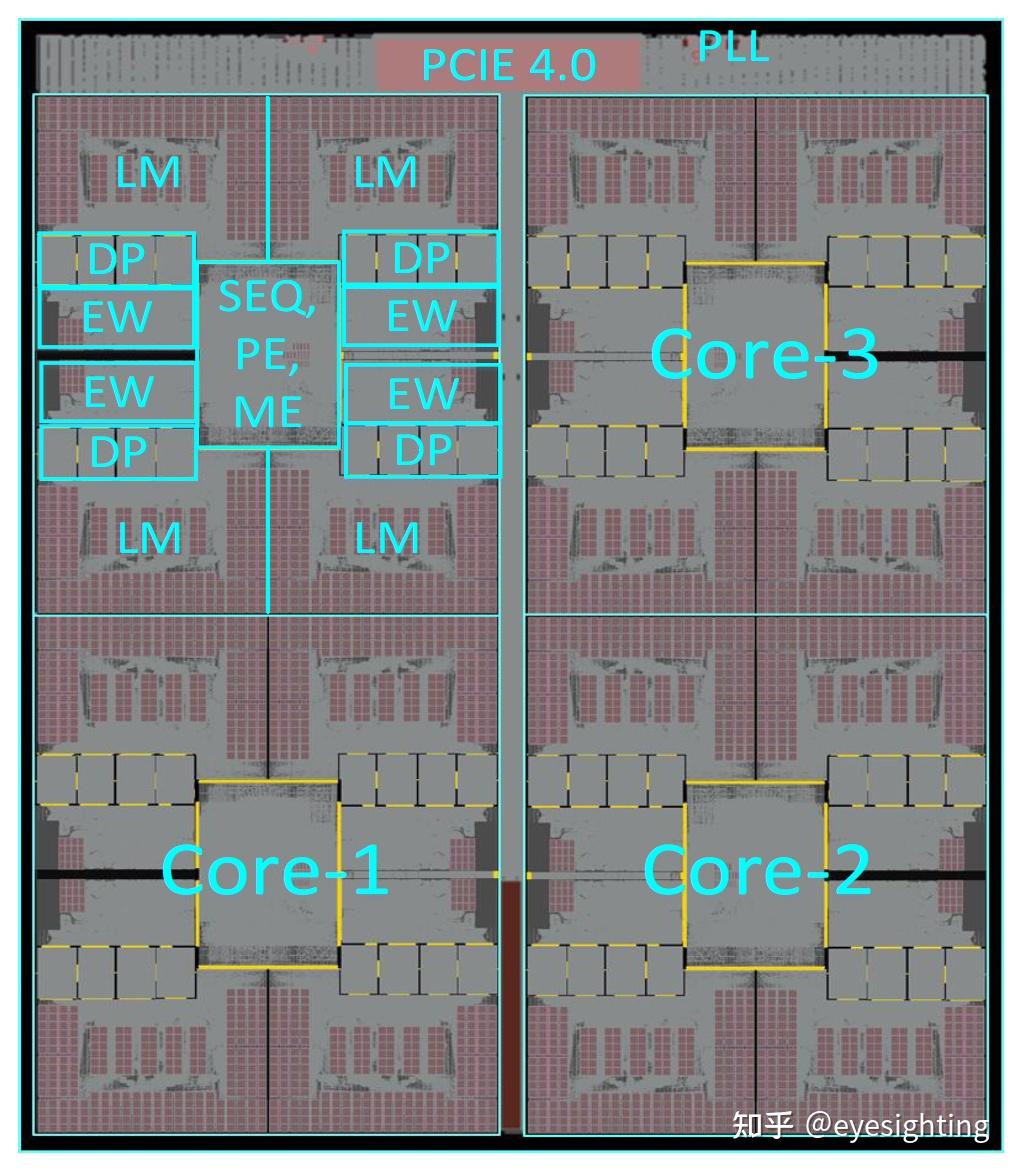

顶层:4 核,带环形总线;命令处理器 (CP);PCIE 第 4 代 X16。

每个核心:张量引擎 (TE);池化引擎(PE);内存引擎(ME)。

仅 SRAM:192MB 本地内存 (LM);分布式共享;无DDR。

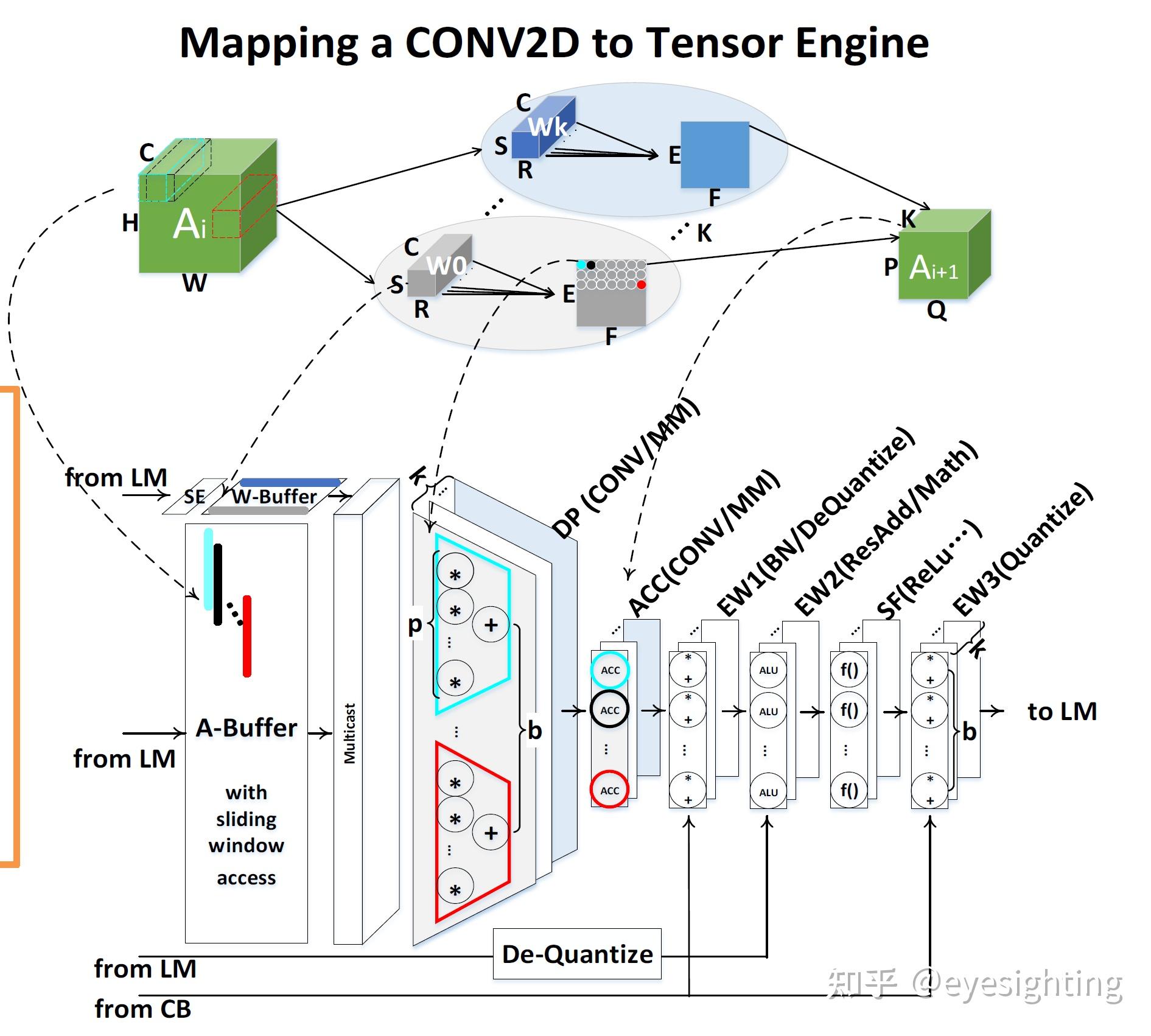

张量引擎

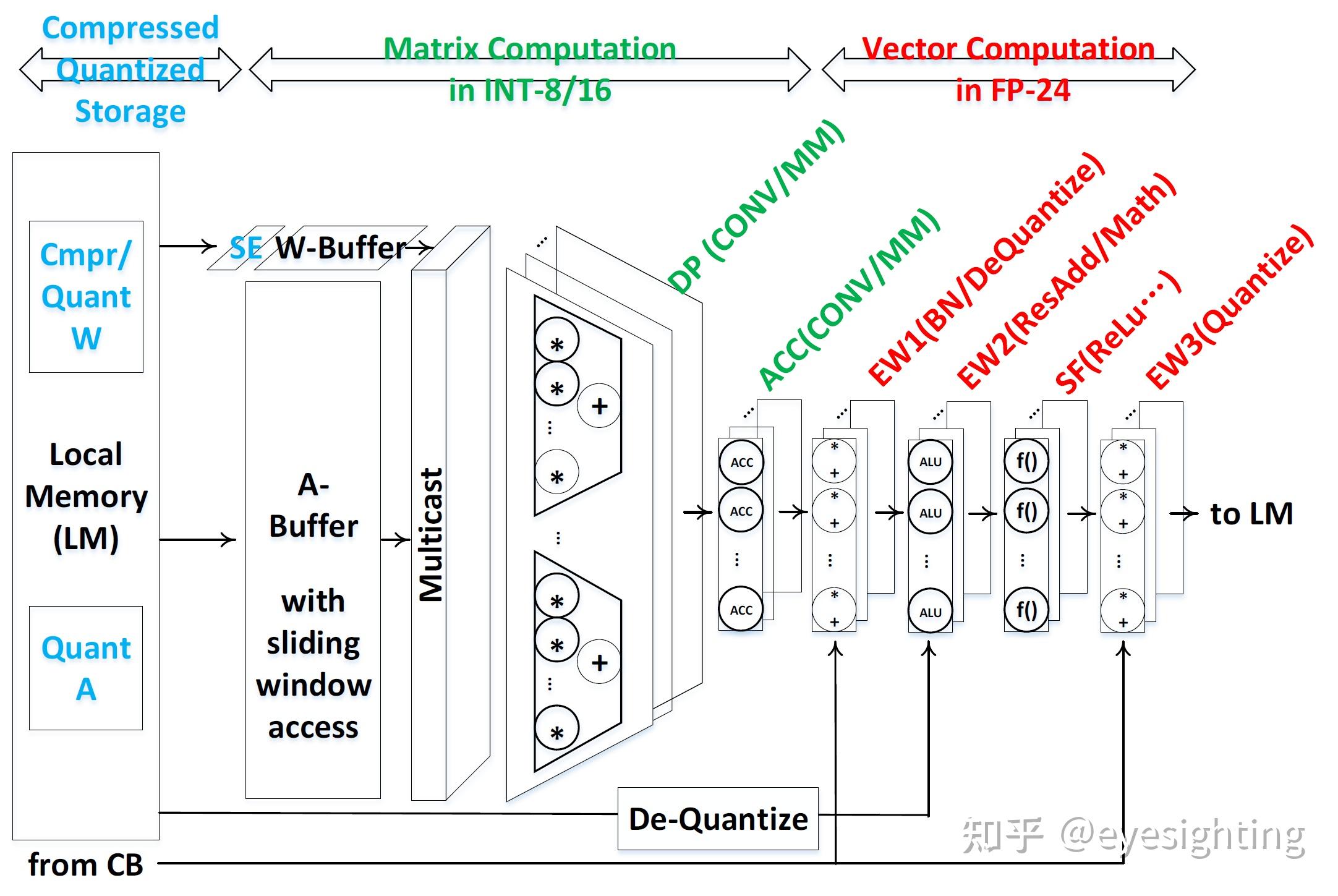

权量+激活固定

数据复用:通过W 缓冲区、A 缓冲区、组播

避免 img2col():通过滑动窗口访问

融合OP:CONV-BN-ResidualADD-ReLU

将 CONV2D 映射到张量引擎

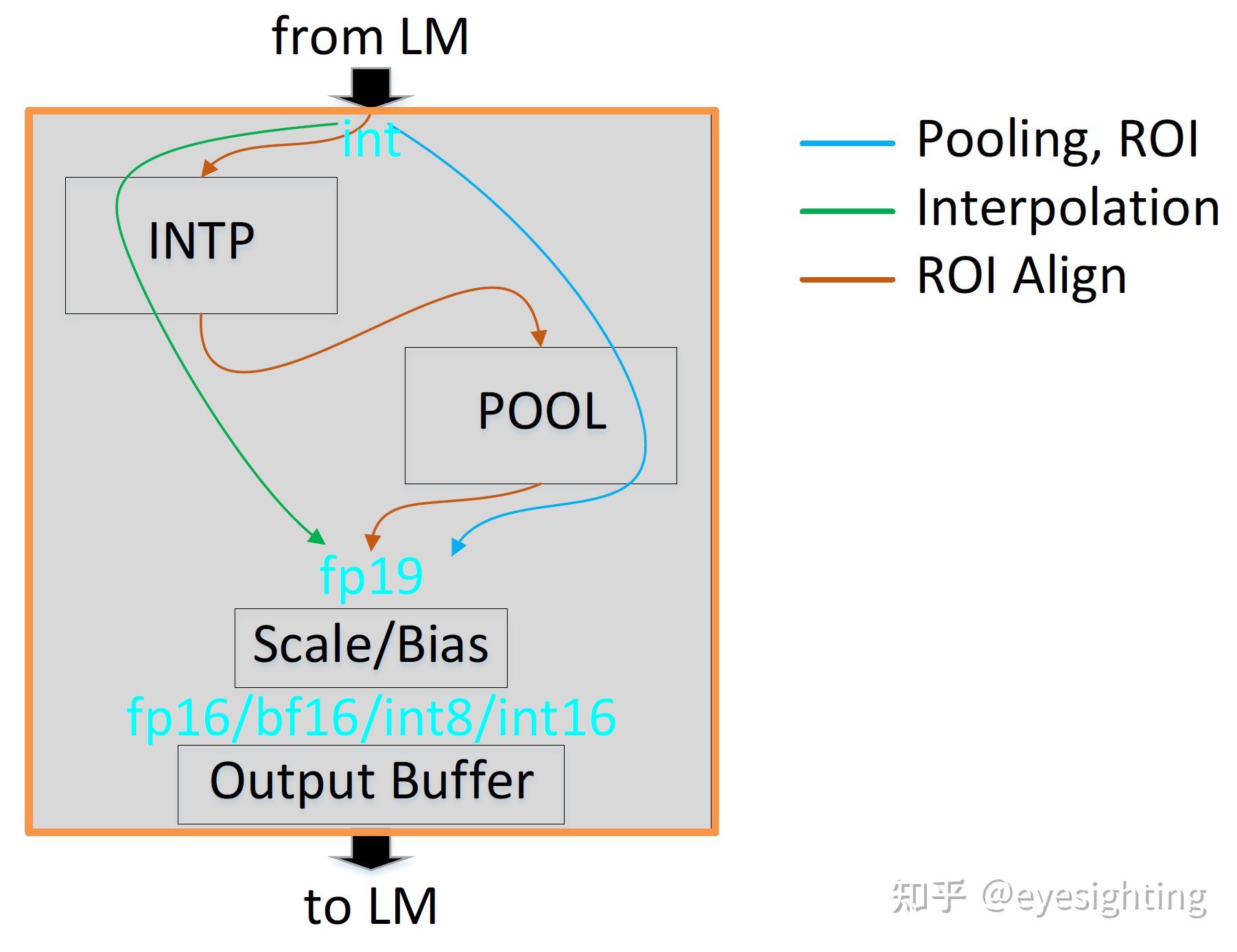

池化引擎

池化单元:POOLs、ROIs,ROI_align 2

INTP单元:插值、ROI_align 1

比例/偏差单位:缩放/偏置操作,数据格式化

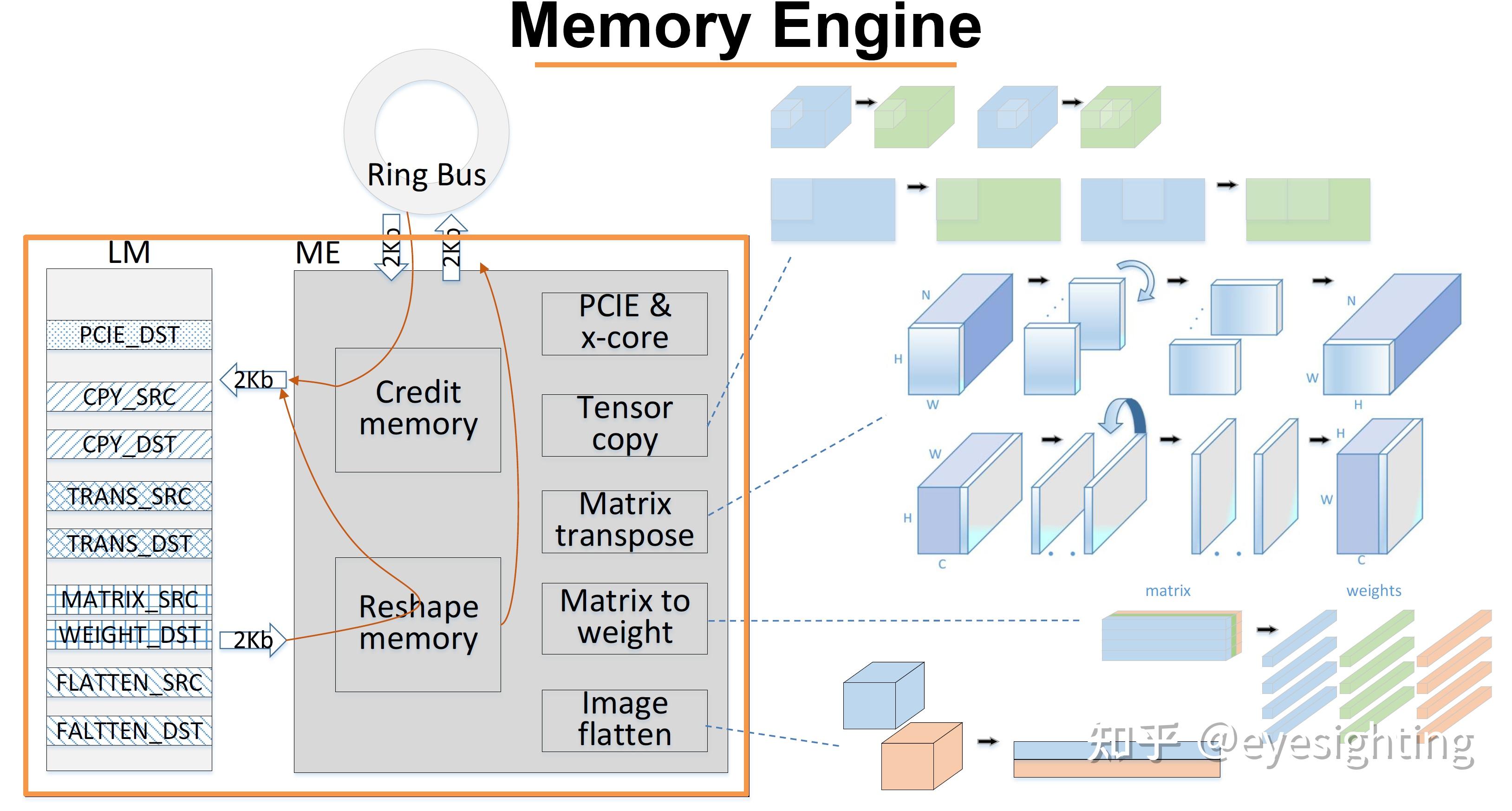

内存引擎

环形总线

板端内存、重塑内存

PCIE和x-core、张量复制、矩阵转置、矩阵到权重、图像展平

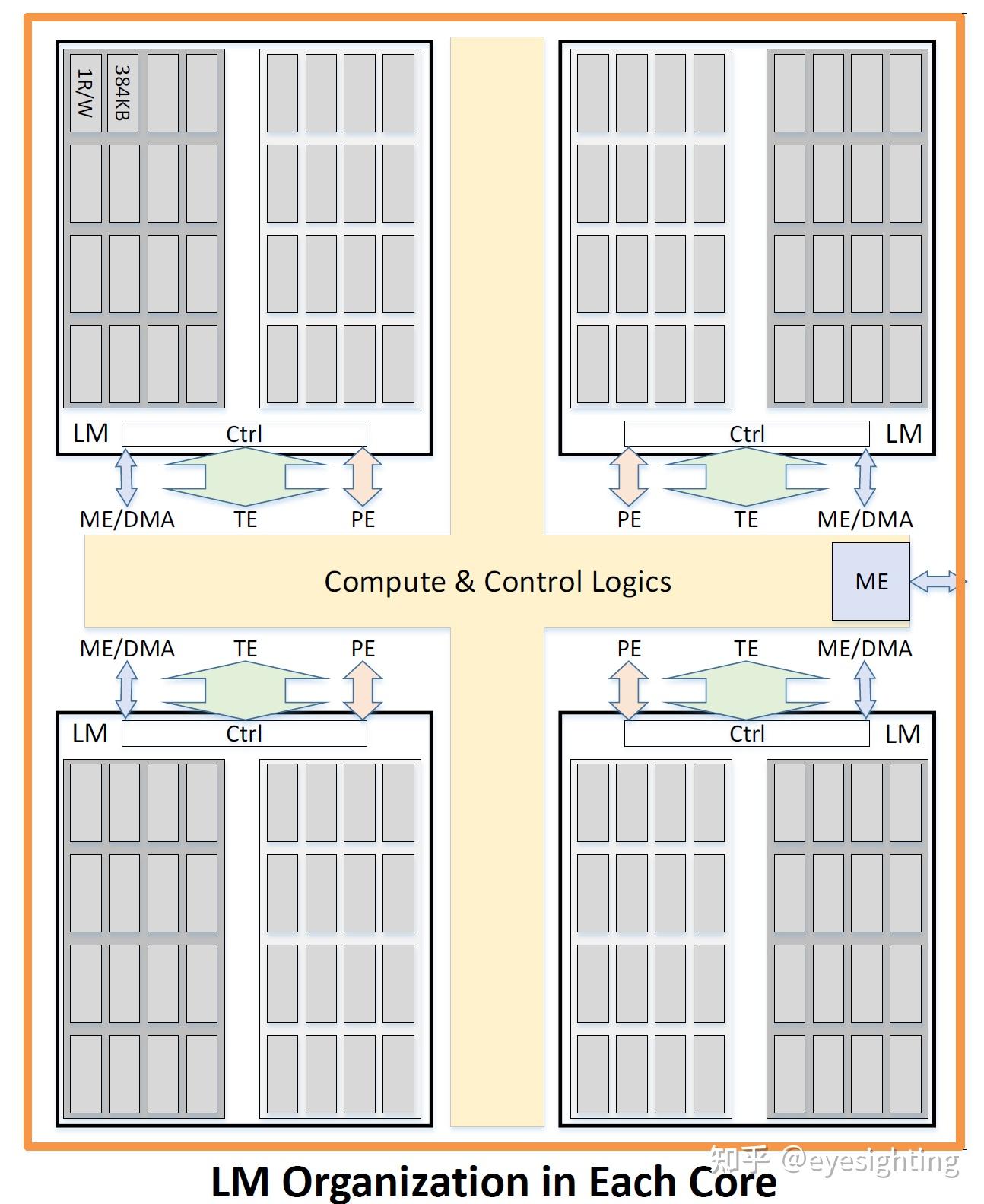

192MB 片上 SRAM

1个R/W SRAM模块:高密度、低功率

2块W&A:每个区块有16个模块

4个集群:分布式共享

4个核心中的每一个都有48MB:通过ME和环形总线跨核心进行内存复制

压缩和量化存储/处理

压缩模型:Sparsity Engine可使用位掩码打开包装,修剪是可选的

量化计算和存储:

矢量单元w/FP-24:1sign.8exp.15man

INT-8/16中的矩阵计算

FP-24中的矢量计算

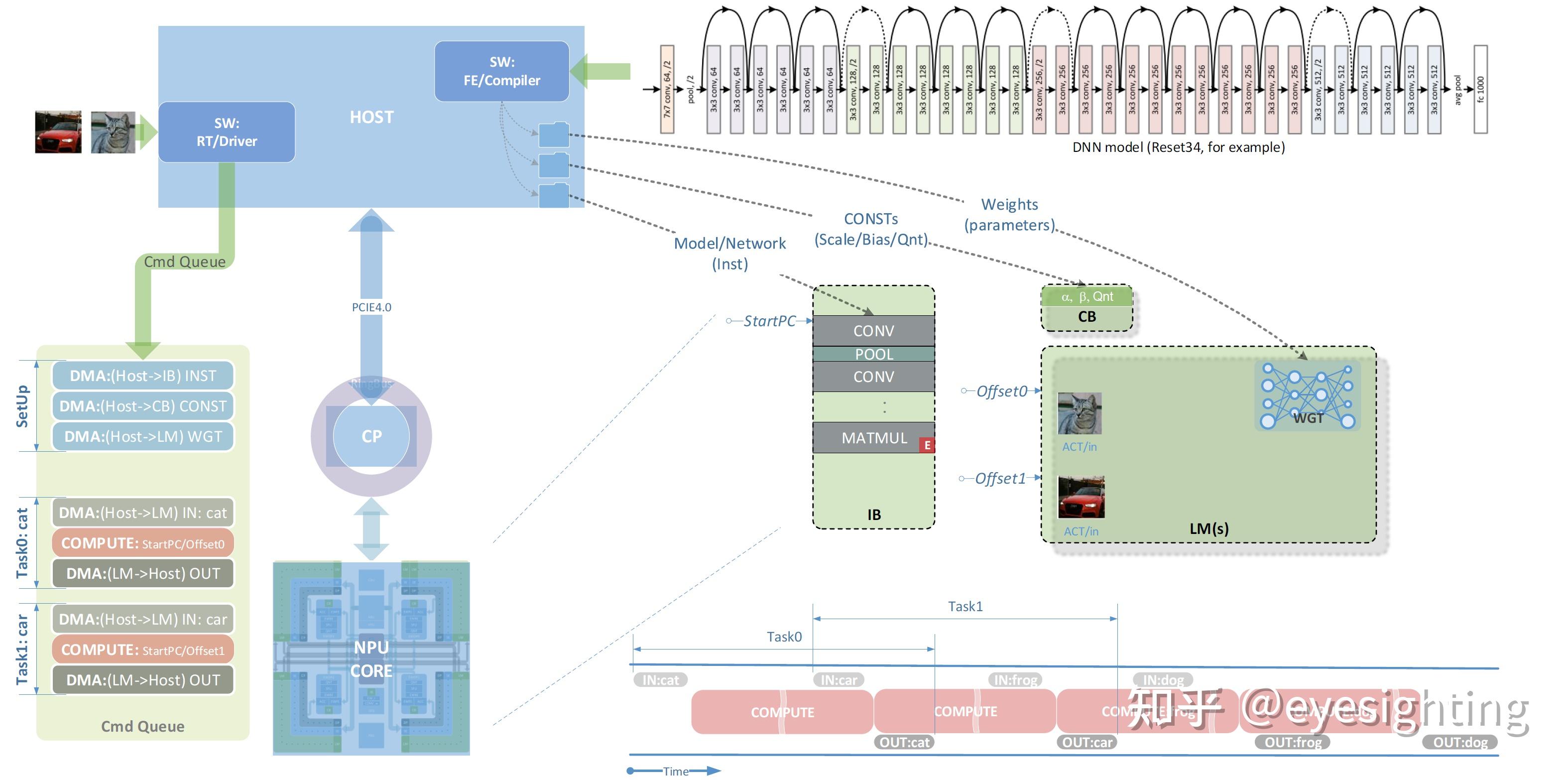

命令级工作流

DNN模型:

SW:FE/编译器:

模型网络

consts:scale、bias、qnt

权重参数

SW:RT/驱动程序:

Cmd队列:

NPU Core:

Task0、Task1、Task2

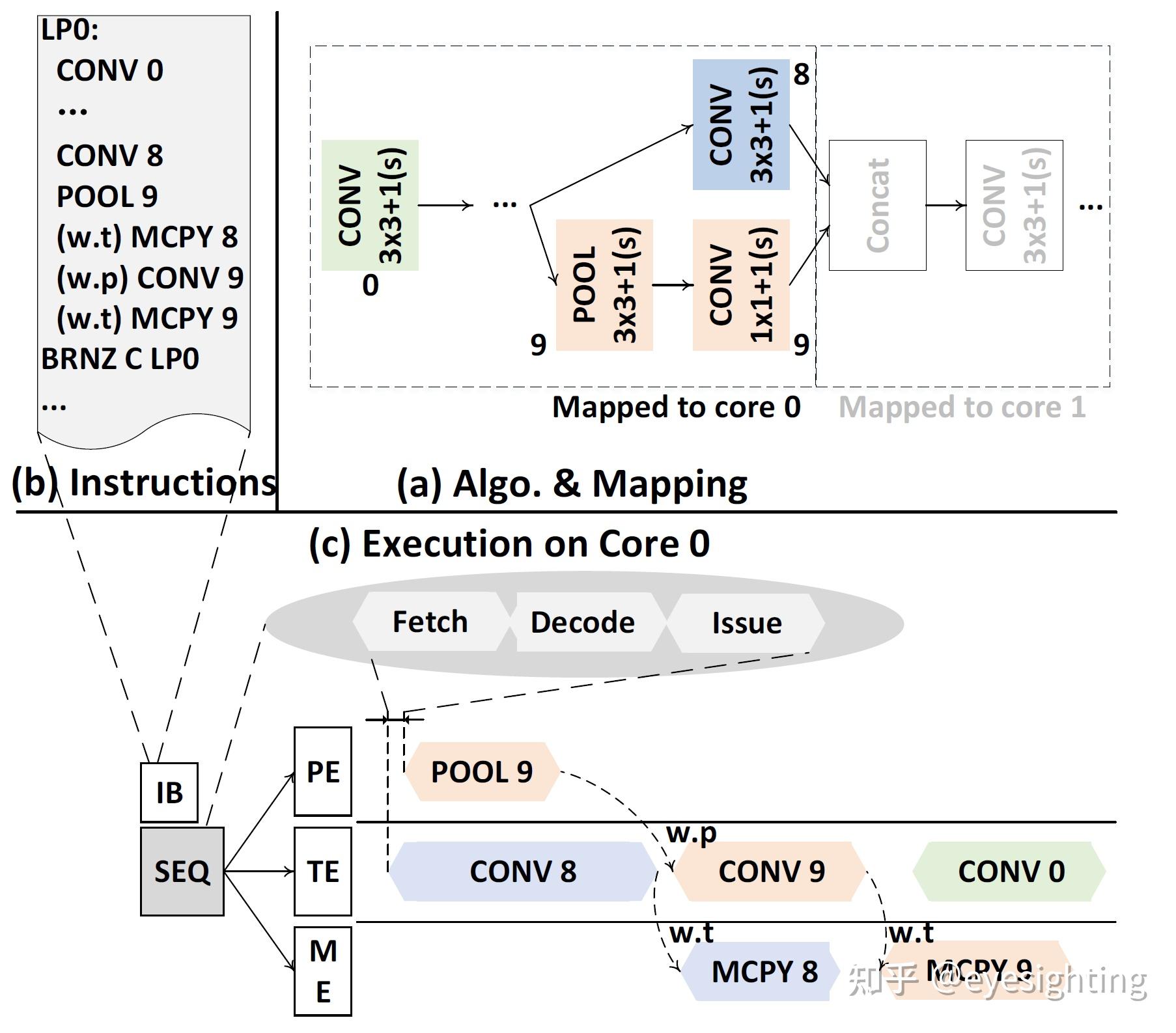

指令级工作流

特定于域的指令集

–类似CISC,操作融合

–张量级别的粗粒度数据(HW分解和ctr)

3个引擎之间的同步

–指令中的嵌入位

–硬件依赖性检查器

工作流

(a) 算法映射

(b) 指令

(c) 在核心0上执行

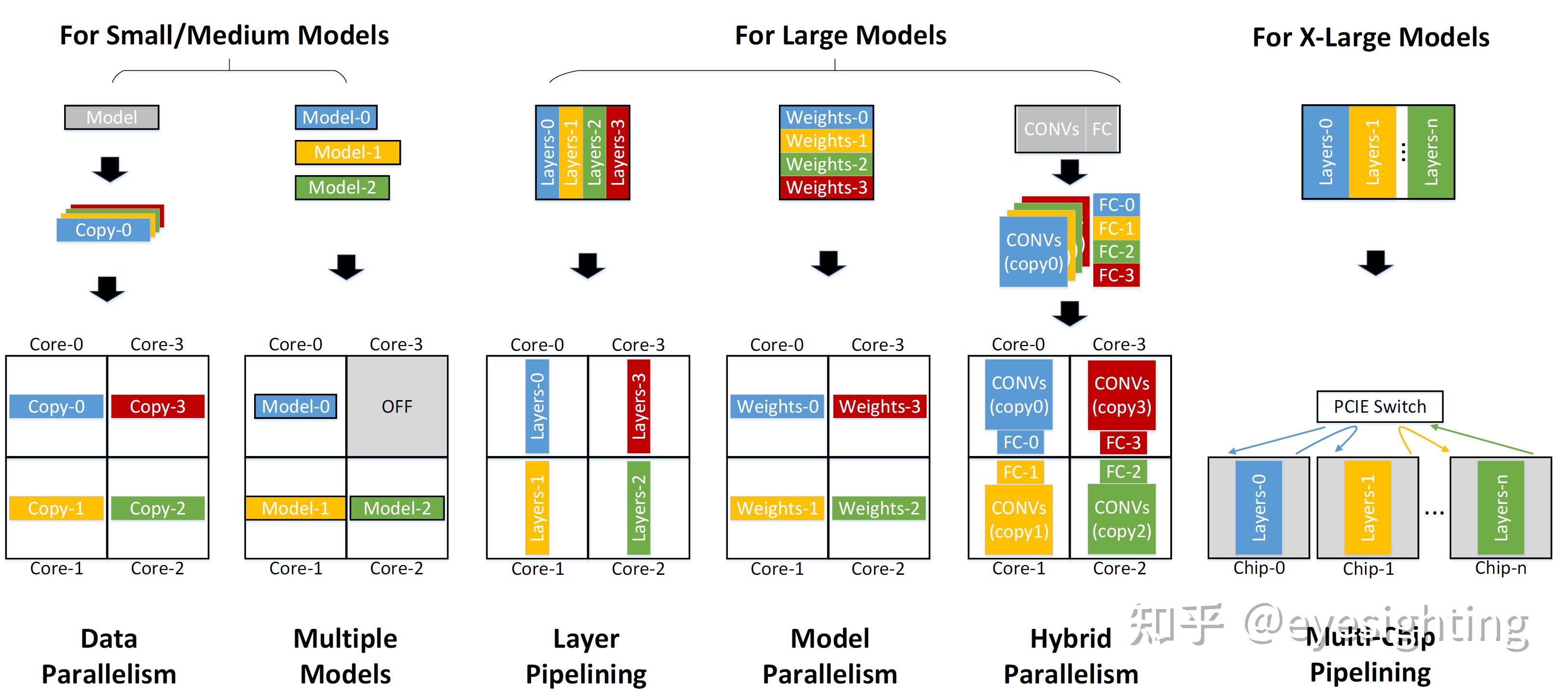

可扩展任务映射

适用于中小型:数据并行性、多个模型

对于大型型号:层流水线、模型并行、混合并行

对于X-Large型号:多芯片流水线

实施

峰值性能(INT8 TOPS)

频率(MHz)

TDP(瓦特)

面积(毫米^2)

工艺(nm)

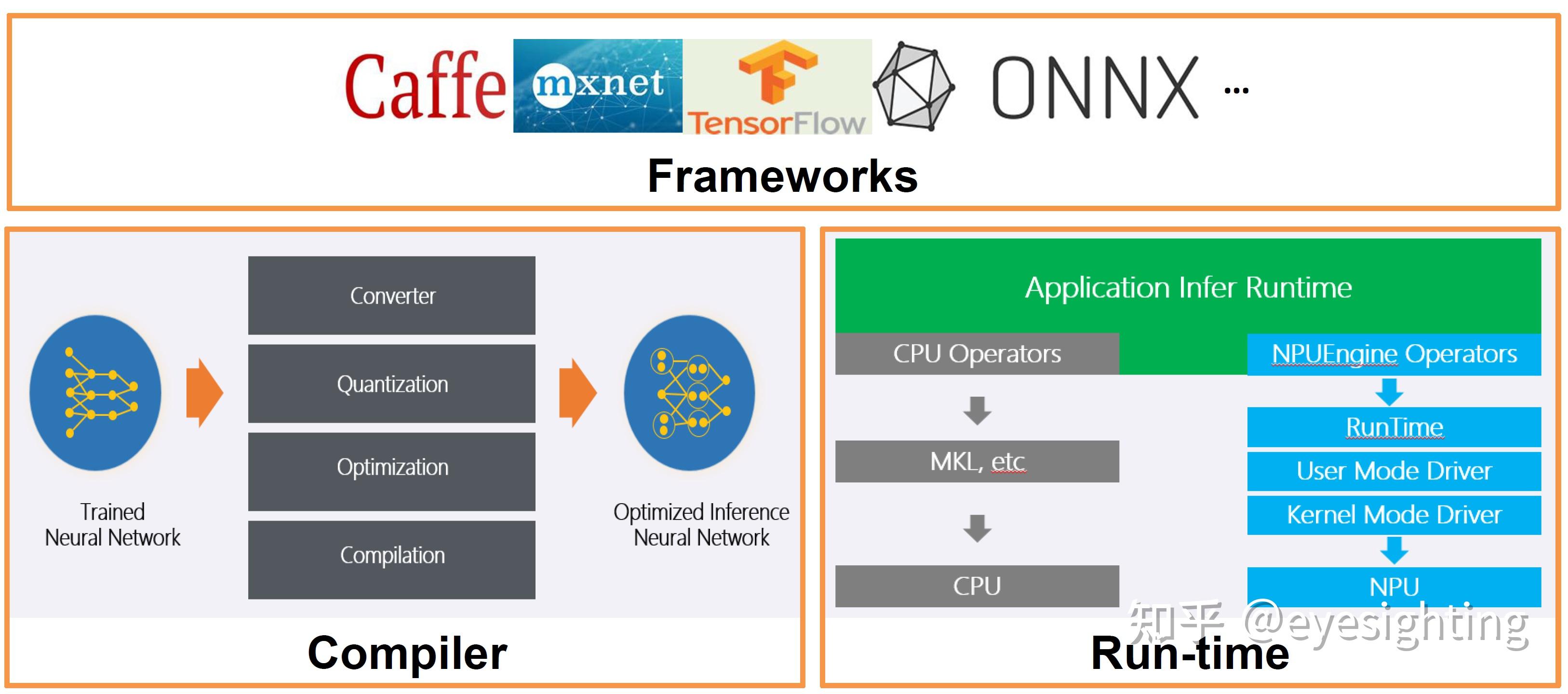

软件栈

Caafe、MXNet、TensorFlow、ONNX

编译器

训练后网络

转换、量化、优化、编译

优化后的推理网络

应用程序推理运行

CPU:CPU算子、MLK、CPU

NPU:NPU引擎算子、运行态、用户态驱动、内核态驱动、NPU

软件栈

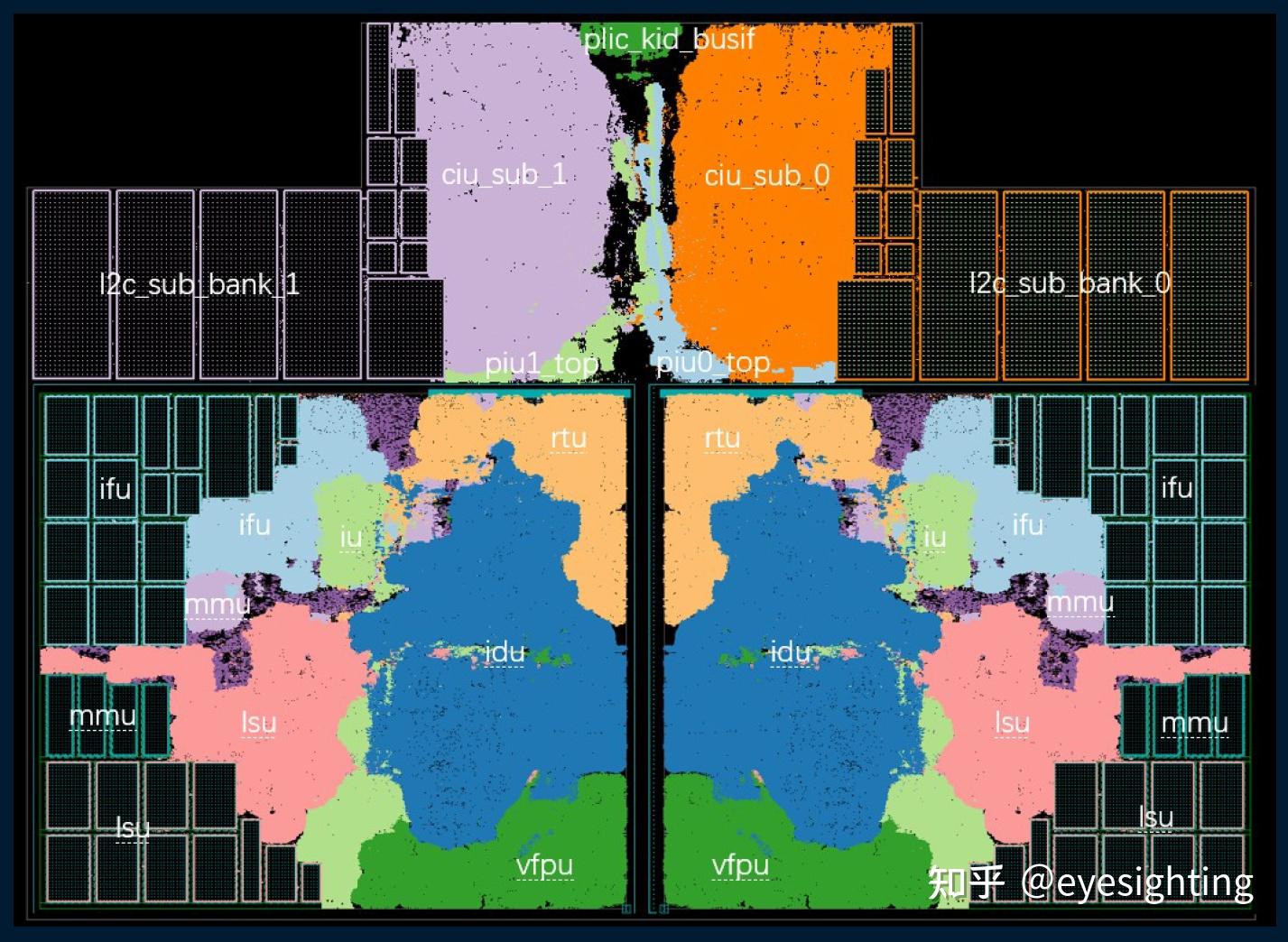

2.玄铁910

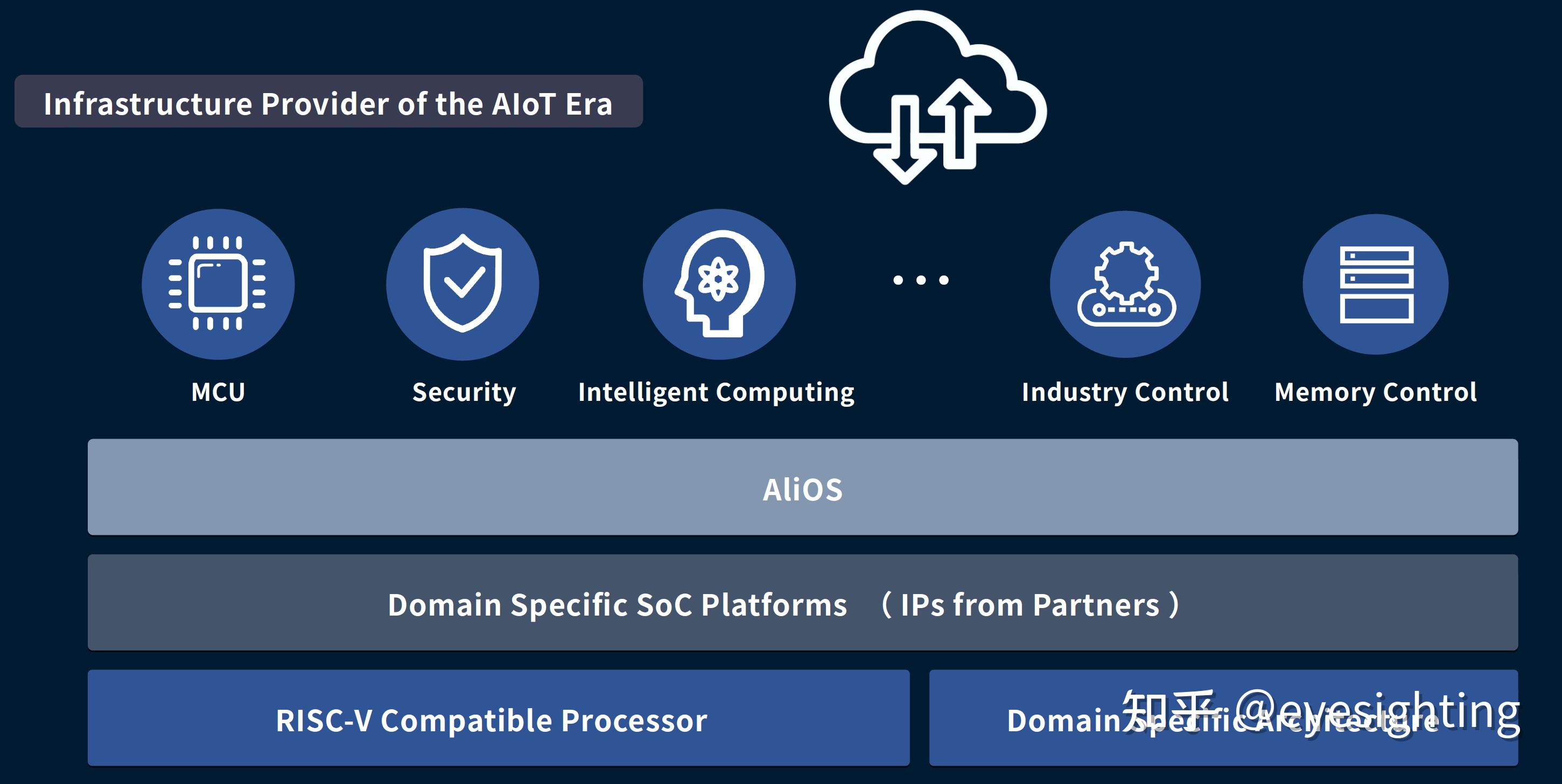

构建AIoT时代的芯片基础设施

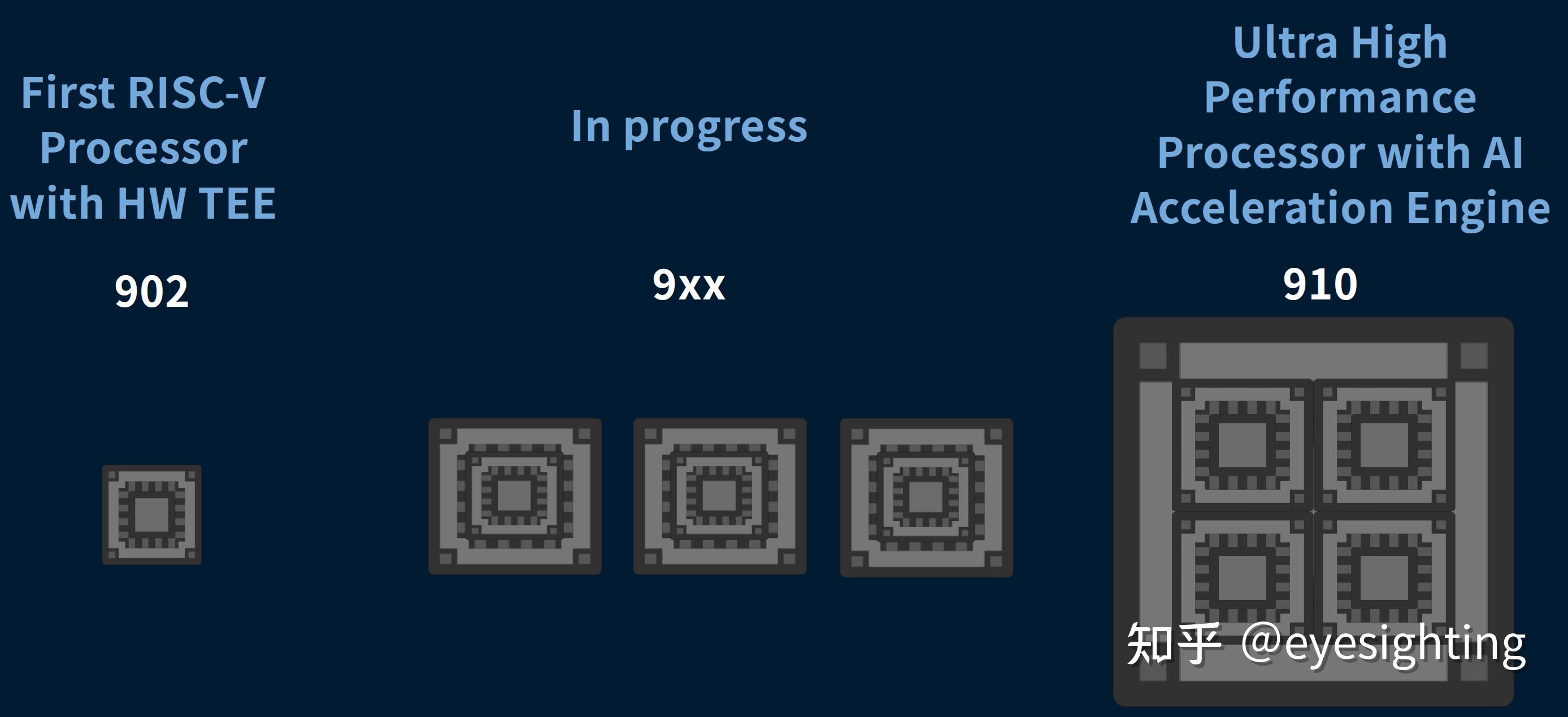

玄铁-不断发展的处理器架构

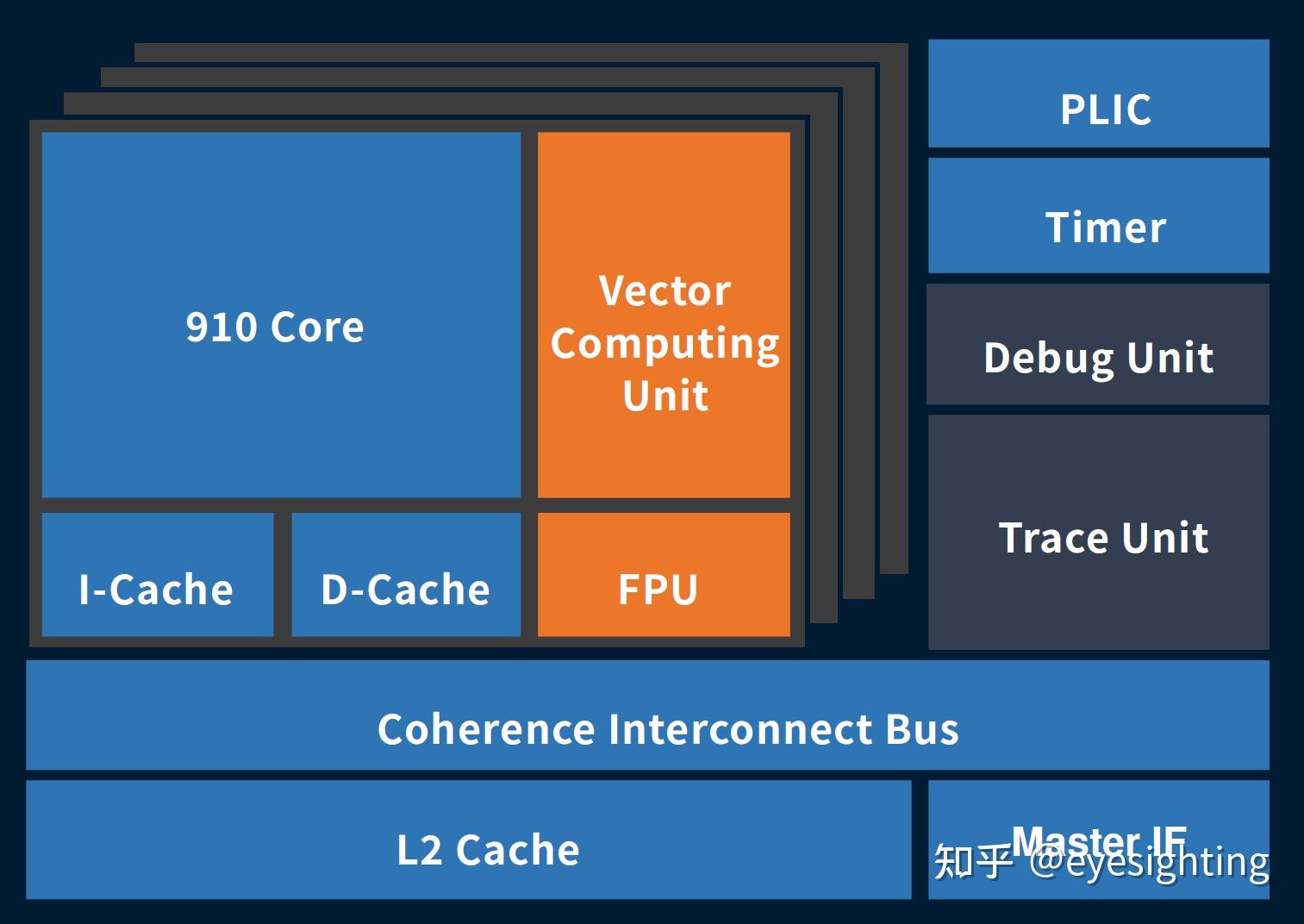

超高性能架构-玄铁910

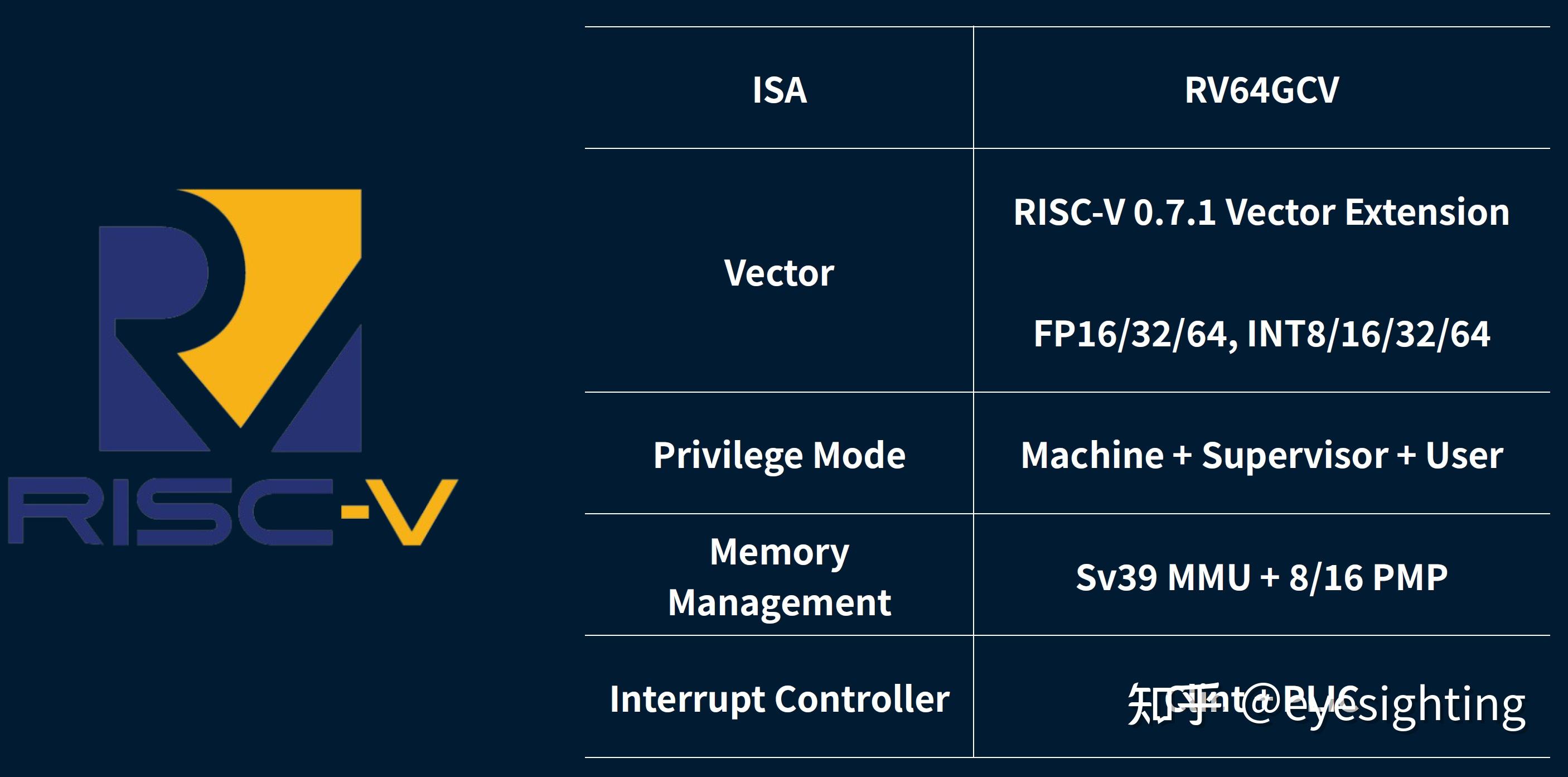

RISC-V RV64GCV:

基于集群的多核架构

每个集群 1/2/4 个核心

32KB/64KB L1 D$; 32KB/64KB L1 I$

64位、12级、乱序

3 次解码,8 次发布

双问题无序内存访问

高性能混合分支处理

多模式动态数据预取

用于人工智能加速的矢量引擎

人工智能、边缘服务器、工业控制、ADAS

兼容RISC-V规范

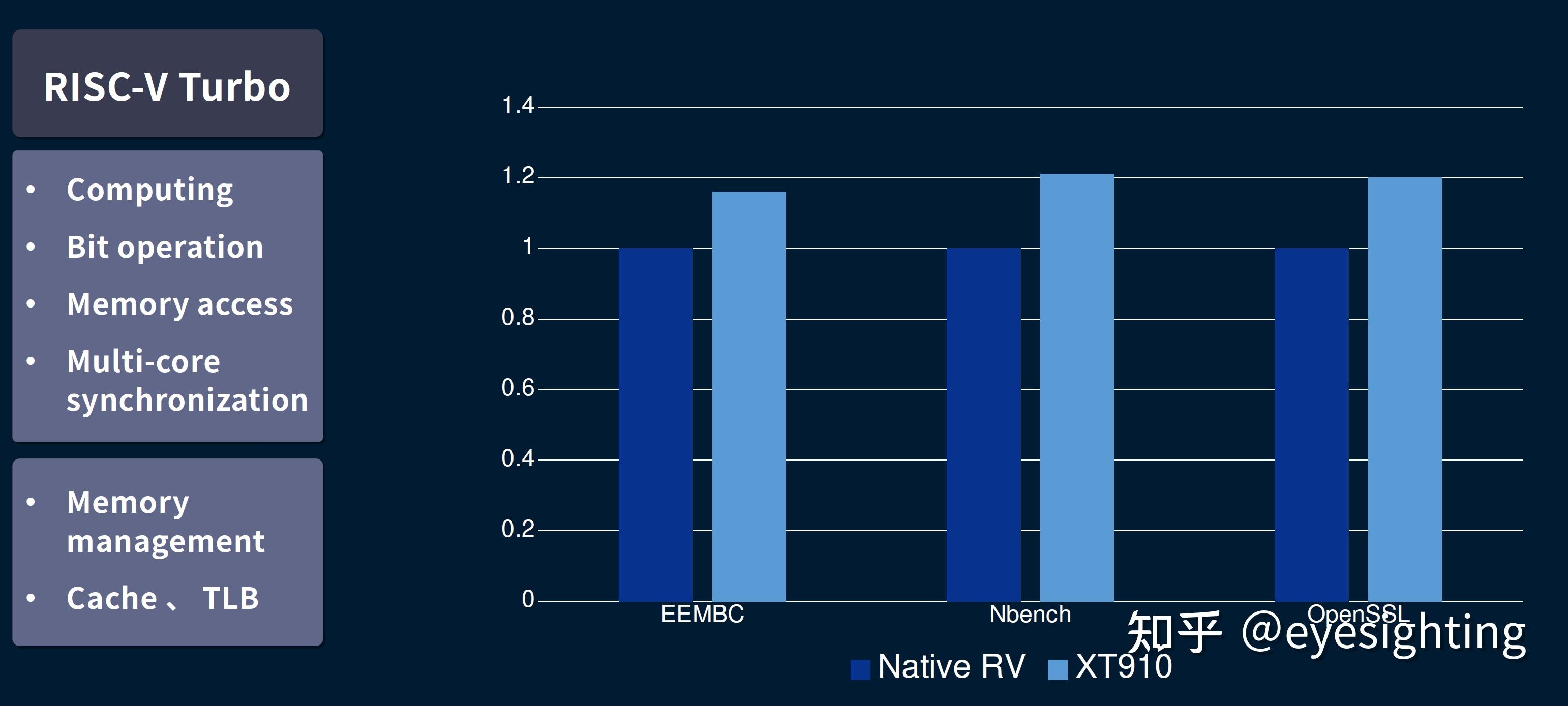

扩展增强 – RISC-V Turbo

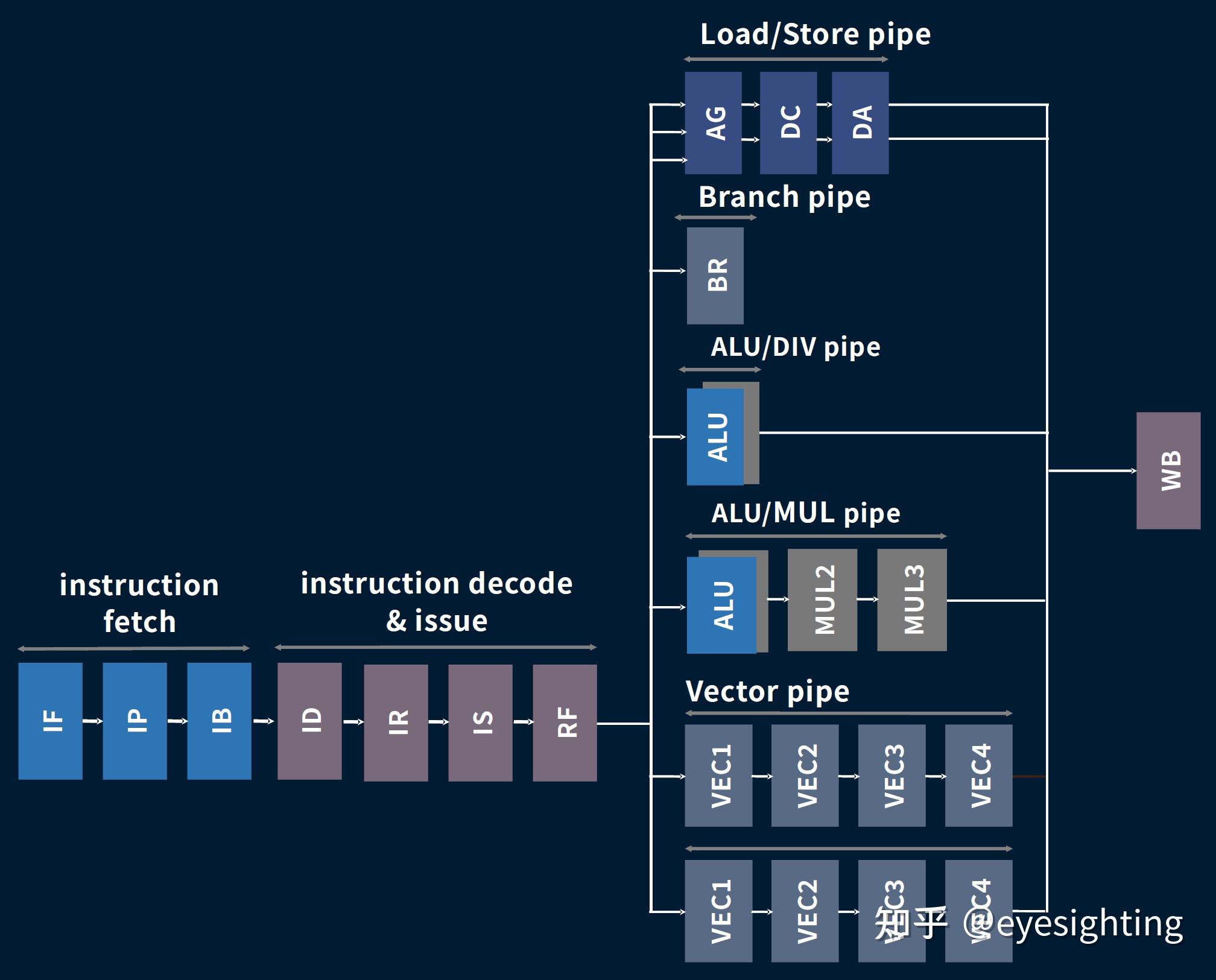

深层超标量无序管道

前端

获取 8 条指令/周期;每个周期解码 3 条指令;第 8 期指令/周期;

后端

无序内存访问;专用分支处理;乱序向量计算

无序管道

取指令;指令译码及发出;装载/存储管道

支管道:ALU/DIV管道;ALU/MUL管道;矢量管道

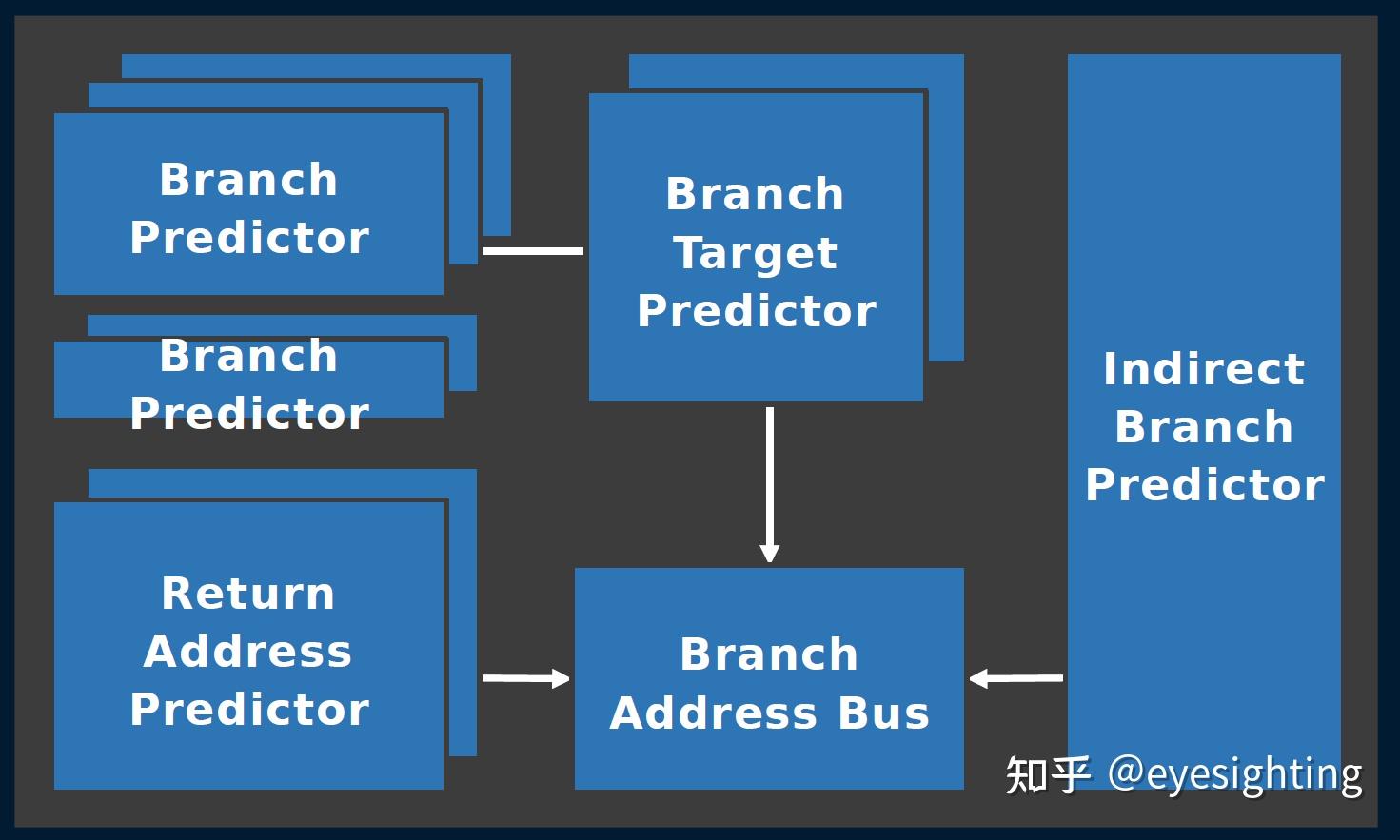

具有混合预测功能的取指单元

混合多模式分支预测

分支方向预测

分支目标预测

返回地址预测

间接分支预测

高带宽并行提取

128位读取

并行封装多达 8 条指令

指令缓存方式预测

循环加速

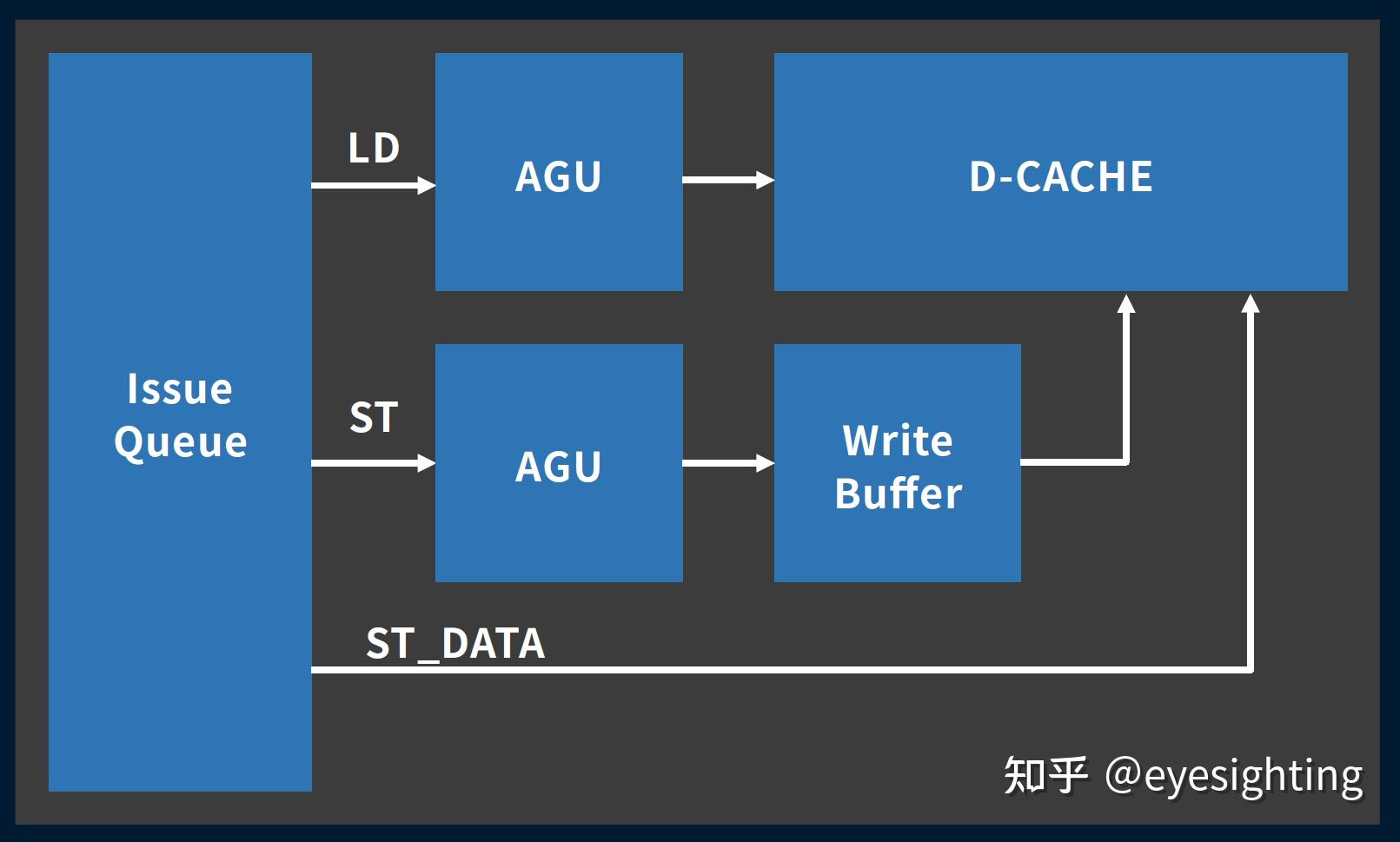

双问题无序加载存储单元

无序双重发行

加载/存储地址管道;独立存储数据管道;推测失败预测。

快速完成加载/存储

3 个循环加载使用;1 个周期存储执行。

强大的预取能力

多模式和多流;虚拟地址和物理地址预取;可配置的预取容量。

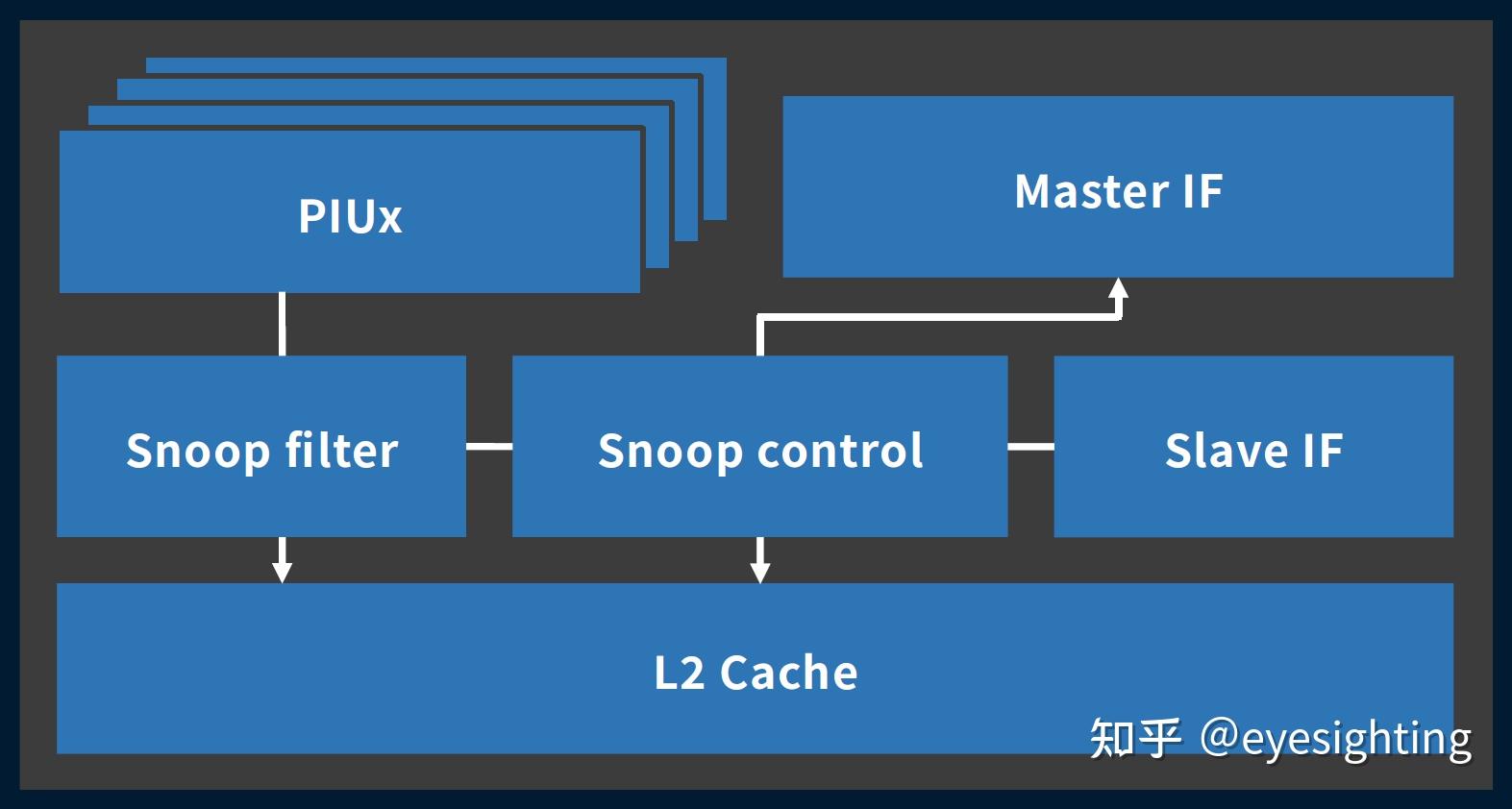

高效多核互联

解耦处理器接口单元 (PIUx)

MOESI 一致性协议

基于目录的架构

支持探听过滤器

可配置的L2缓存,高达8MB

支持 ECC

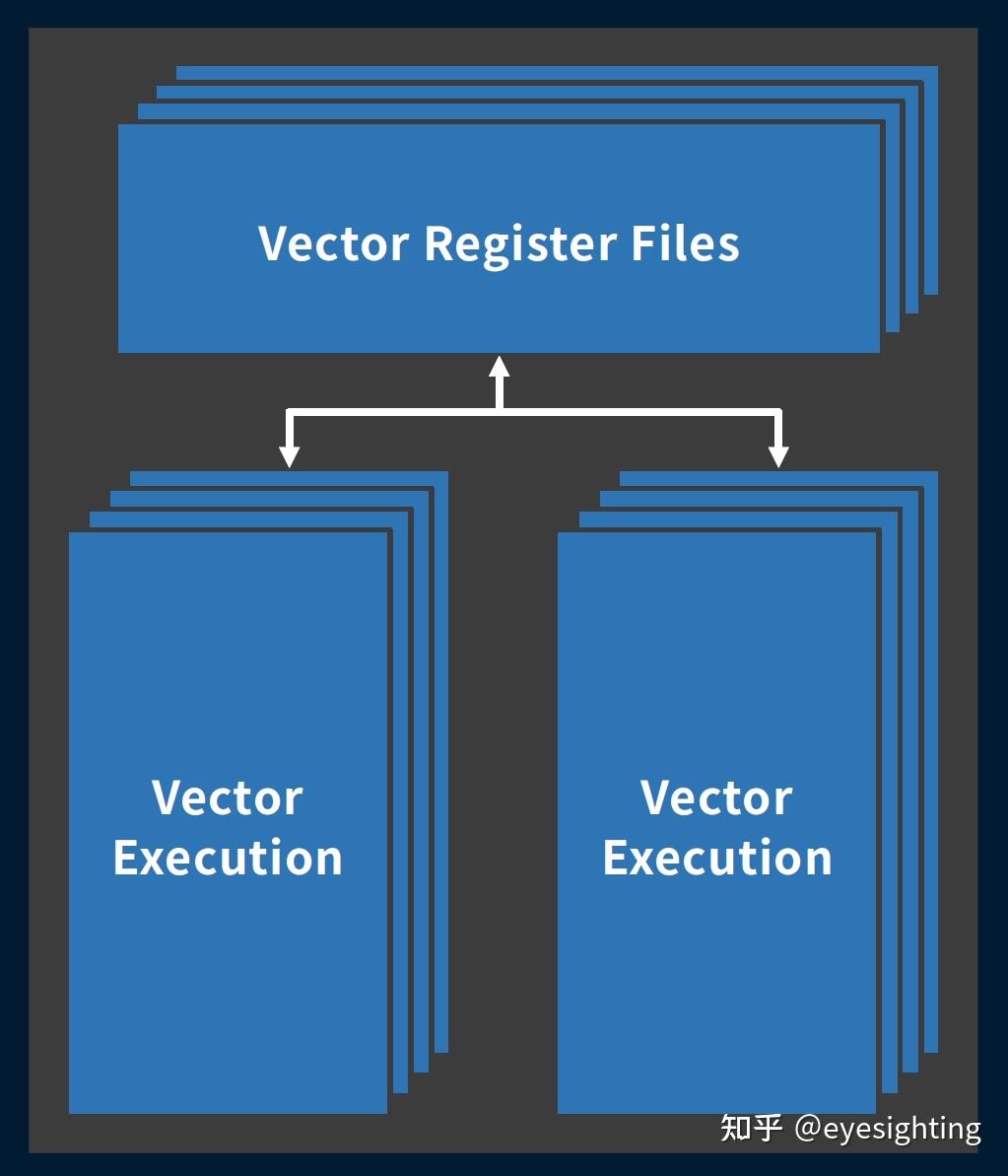

AI优化矢量计算引擎

兼容 RISC-V 0.7.1 矢量扩展

支持 FP16/32/64、INT8/16/32/64

256 位操作宽度,VL = 128 和 2 个流水线

每个周期两个 128 位向量 ALU 操作

每个周期 1 个 128 位向量加载和 1 个 128 位向量存储

直接访问向量加载和向量存储上的L1$

双发出乱序向量执行管道

每个集群超过 300GFLOPS 的 FP16 计算能力(32 FLOPS/核心/周期 x 2.5 GHz x 4 核心)

扩展至 FP32 时,FP16 计算能力减半

AISC实施

工艺技术:台积电12nm FinFET

工作频率:2.0 GHz a ~ 2.5 GHz b

a.LVT 6T-turbo STD 电池,0.8V VDD,TT 85oC

b.30% ULVT 标准电池,1.0V VDD,TT 85oC

每芯面积(不含L2$):0.6 mm2(无VEC),0.8 mm2(有VEC)

总结

与Google、百度类似,阿里也在自研云服务器芯片,已经大规模上应用于阿里云和数据中心。

参考文献

HC32-2022:含光800:https://www.hc32.hotchips.org/assets/program/conference/day2/HotChips2020_ML_Inference_Alibaba_HanguangNPU_final.pdf

HC32-2020:玄铁910:https://www.hc32.hotchips.org/assets/program/conference/day1/HotChips2020_Edge_Computing_Xuantie910_v1.1.pdf

ISCA-2020:玄铁910:https://ieeexplore.ieee.org/document/9138983

原文链接:https://zhuanlan.zhihu.com/p/646793418

评论 ( 0 )