引入

近些年来,深度学习网络不断兴起。数据运算量越来越大,对处理器并行处理能力要求越来越高。传统的通用处理器CPU受摩尔定律的影响,已经不能满足大规模的数据处理了。故而,专用AI处理器的设计再一次引起了人们的广泛关注。本文中,作者介绍几种常见类型的AI芯片。

一、指令集架构的控制流处理器

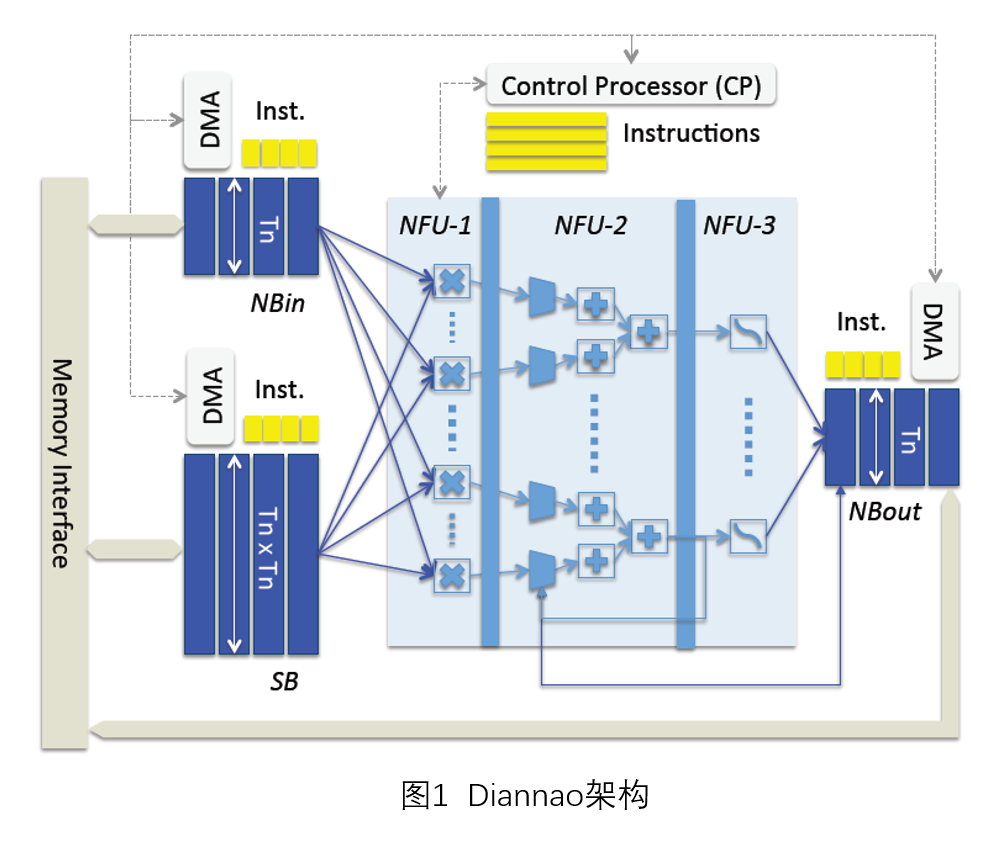

这类处理器会为深度学习应用专门定义一类指令集,用指令集驱动的方式指引处理器的执行。指令集驱动的方式常见于通用处理器CPU的设计之中。2014年,寒武纪提出了Diannao[1]架构处理器。这是一个真正的面向深度学习(CNN、DNN网络)的专用指令集架构处理器。该处理器采用类冯诺依曼架构,将控制、计算和存储单元分离实现。该处理器具有非常优秀的性能功耗比,由此开启了在专用处理器上执行AI应用的先河。

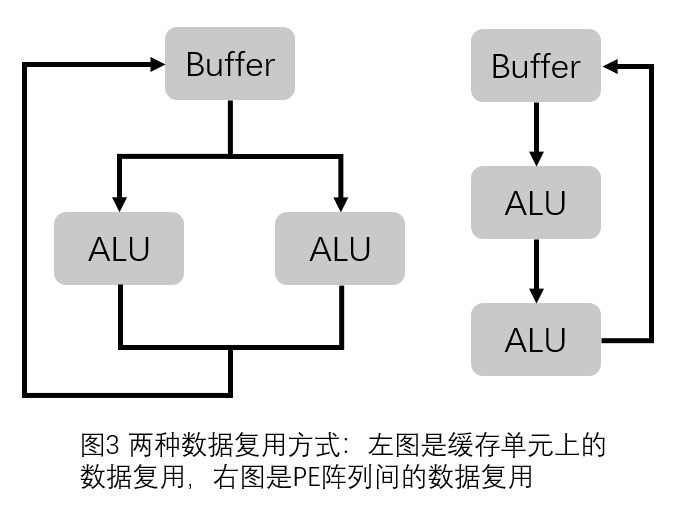

控制流处理器的数据复用通常发生在片上缓存单元。数据传输过程为:缓存单元上的数据被复制多份,再以广播的形式发送给多个并行处理的运算单元(PE)上。这类处理器存在一个问题,一旦PE数目增多,受芯片布线长度限制,处理器就会出现主频瓶颈问题。该类处理器设计起来相对简单,简单就意味着可靠、可拓展性较好。

二、数据流处理器

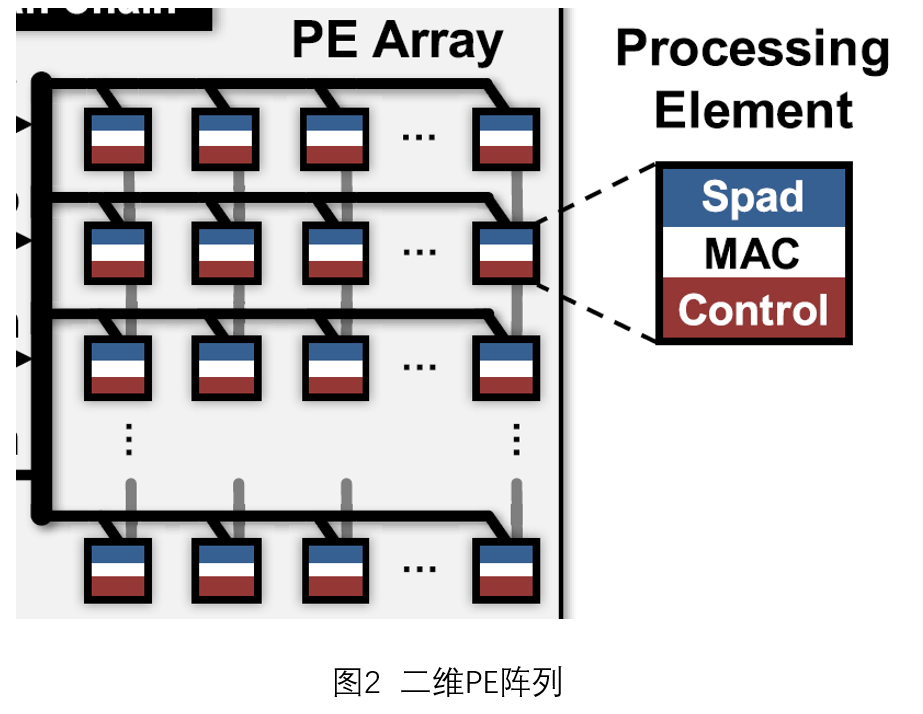

该类处理器的计算行为发生在由数据流驱动的张量处理单元上,目前最常见的张量处理单元是二维的PE阵列,如图2所示。其计算过程如下:神经网络张量会被划分为多个tile,每个tile映射到一个PE上执行运算。一次运算完成后,数据按照某种策略,传播给到其它PE单元中,继续执行运算。上述过程中,数据在PE单元间实现了数据复用。缓存单元上的数据复用和PE单元间的数据复用方式的示意图如图3所示。数据流处理器相比于控制流处理器,能够解决了主频瓶颈问题。

常见的数据流处理器可以分为两类:一类是权值固定(Weight Stationary)的处理器,以Google在2017年提出的TPU1.0[2]为代表。权值固定的架构可以理解为脉动阵列。另一类是输出固定(Output Stationary)的处理器,寒武纪在2015年提出的Shidiannao[3]就是采用输出固定的架构。还有一些其它的数据流架构,比如MIT提出的Eyeriss处理器,采用的是行固定(Row Stationary)架构。数据流架构处理器设计起来相对较难。

三、可重构处理器

可重构处理器以在FPGA上实现的AI加速器为代表。可重构的含义在于:可以根据算法需求,动态重构计算架构,可支持多种数据位宽。FPGA相比于ASIC上的加速器设计,设计周期短。特别是现在有了高层次综合工具,直接用高级语言C/C++语言编写程序后,利用高层次综合工具就可以直接将其转换为硬件描述语言RTL,大大缩短了开发周期,便于算法的快速验证。FPGA是半定制电路,可以看作是在ASIC上进行一层抽象出来的结构。因此其电路布线效率不高,主频相比于ASIC逊色很多。

参考文献

[1] T. Chen, Z. Du, N. Sun, J. Wang, C. Wu, Y. Chen, et al., “DianNao: a small-footprint high-throughput accelerator for ubiquitous machine-learning,” Acm Sigplan Notices, vol. 49, pp. 269-284, 2014.

[2] N. P. Jouppi, C. Young, N. Patil, D. Patterson, G. Agrawal, R. Bajwa, et al., “In-Datacenter Performance Analysis of a Tensor Processing Unit,” pp. 1-12, 2017.

[3] Z. Du, R. Fasthuber, T. Chen, P. Ienne, L. Li, T. Luo, et al., “ShiDianNao: Shifting vision processing closer to the sensor,” in ACM SIGARCH Computer Architecture News, 2015, pp. 92-104.

[4] Y. Chen, T. Krishna, J. S. Emer and V. Sze, “Eyeriss: An Energy-Efficient Reconfigurable Accelerator for Deep Convolutional Neural Networks,” in IEEE Journal of Solid-State Circuits, vol. 52, no. 1, pp. 127-138, Jan. 2017, doi: 10.1109/JSSC.2016.2616357.

Finished.

原文链接:https://www.ngui.cc/el/2916037.html

评论 ( 0 )